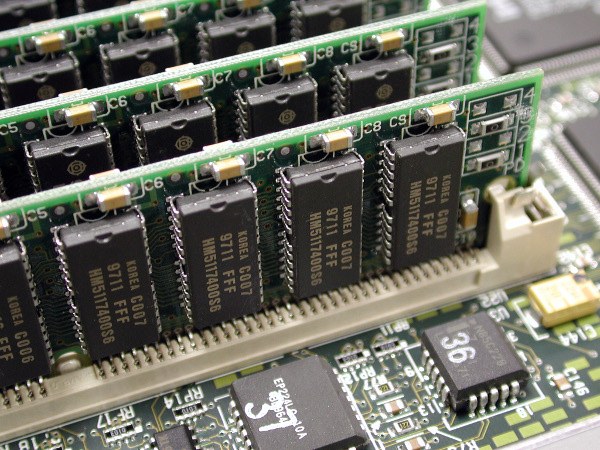

The computer memory (RAM) — volatile memory that contains the components of the OS and running programs. The amount of memory affects how much information it can contain simultaneously, and thus on the number of applications running. Frequency characterizes the speed of the memory, i.e. the number of operations (cycles) per second.

The latency or timings, show the number of cycles spent on internal operations, in other words, the timings characterize a simple memory.

For understanding of those or other timings is more focus on the memory access. Simplified memory chip can be represented in the form of a table, where each cell corresponds to a memory element storing one bit.

When selecting a cell via the address bus is the number of column and row. The first gate pulse is supplied to access the string — RAS (Row Access Strobe), then the momentum of the column access CAS (Column Access Strobe).

After selecting a cell on it are sent to various control pulses — tolerance check to write, write, read or recharge. And between these operations there are delays, which are called timings.

There are four different timing specified by manufacturers of memory modules.

CL (CAS latensy) – CAS-delay is the wait between the CAS pulse and the beginning reader. In other words, the number of cycles required to read the cells if the line is already open.

T RCD (Row Address to Column Address Delay) – delay between RAS and CAS pulses. The timing shows the time between the opening line and the opening of the column.

T RP (Row Precharge Time). The timing delay between the pulse to close the active row and the RAS pulse on the opening of the next.

The sum of these values characterizes the delay between reading specific memory locations, if opened another line. Manufacturers often specify these three parameters, but sometimes you can see the fourth - T RAS.

T RAS (Row Active Time) – the number of cycles between RAS-impulse and momentum closing line (Precharge), that is, the update time of the row. Usually T RAS equal to three previous timings.

For convenience, timings lead without the designation using the hyphen, for example, 2-2-2 or 2-2-2-6.

The progenitor of computer memory was created in 1834 by Charles Babbage. It's a mechanical device, referred to as "the Warehouse" (store), retained intermediate results of calculations in the "Analytical machine".

The latency or timings, show the number of cycles spent on internal operations, in other words, the timings characterize a simple memory.

The principle of memory access

For understanding of those or other timings is more focus on the memory access. Simplified memory chip can be represented in the form of a table, where each cell corresponds to a memory element storing one bit.

When selecting a cell via the address bus is the number of column and row. The first gate pulse is supplied to access the string — RAS (Row Access Strobe), then the momentum of the column access CAS (Column Access Strobe).

After selecting a cell on it are sent to various control pulses — tolerance check to write, write, read or recharge. And between these operations there are delays, which are called timings.

Types timings

There are four different timing specified by manufacturers of memory modules.

CL (CAS latensy) – CAS-delay is the wait between the CAS pulse and the beginning reader. In other words, the number of cycles required to read the cells if the line is already open.

T RCD (Row Address to Column Address Delay) – delay between RAS and CAS pulses. The timing shows the time between the opening line and the opening of the column.

T RP (Row Precharge Time). The timing delay between the pulse to close the active row and the RAS pulse on the opening of the next.

Sometimes you can meet the entry type 6-6-6-18-24. Here, the fifth number indicates the timing Command rate — the delay between the pulse on the chip select module memory and activating a row.

The sum of these values characterizes the delay between reading specific memory locations, if opened another line. Manufacturers often specify these three parameters, but sometimes you can see the fourth - T RAS.

T RAS (Row Active Time) – the number of cycles between RAS-impulse and momentum closing line (Precharge), that is, the update time of the row. Usually T RAS equal to three previous timings.

For convenience, timings lead without the designation using the hyphen, for example, 2-2-2 or 2-2-2-6.